PROGRAMMABLE CONTROLLERS

### FX20 SUPPLEMENTARY PROGRAMMING MANUAL

THE FX20 PROGRAMMABLE CONTROLLER

### FX2C Supplementary Programming Manual

Manual number:

JY992D50201

Print reference:

HI-IB-151-A9501 (SEN) (A1)

Manual revision:

Α

Date:

January 1995

### Foreword

- This manual contains text, diagrams and explanations which will guide the reader in the correct programming and operation of the PC.

- Before attempting to install or use the PC this manual should be read and understood.

- If in doubt at any stage of the installation of the PC always consult a professional electrical engineer who is qualified and trained to the local and national standards which apply to the installation site.

- If in doubt about the operation or use of the PC please consult the nearest Mitsubishi Electric distributor.

- This manual is subject to change without notice.

### **FAX BACK**

Mitsubishi has a world wide reputation for its efforts in continually developing and pushing back the frontiers of industrial automation. What is sometimes overlooked by the user is the care and attention to detail that is taken with the documentation. However, to continue this process of improvement, the comments of the Mitsubishi users are always welcomed. This page has been designed for you, the reader, to fill in your comments and fax them back to us. We look forward to hearing from you.

| Fax numbers:    |                              | Your name:                                       |

|-----------------|------------------------------|--------------------------------------------------|

| Mitsubishi Ele  | ctric                        |                                                  |

| America         | (708) 298-1834               | Your company:                                    |

| Australia       | (02) 638 7072                |                                                  |

| Germany         | (0 21 02) 4 86-1 12          | Your location:                                   |

| South Africa    | (0111) 444-8304              |                                                  |

| United Kingdo   | m(01707) 278695              |                                                  |

| Please tick the | e box of your choice;        |                                                  |

| What condition  | n did the manual arrive in?  | ☐ Good ☐ Minor damage ☐ Unusable                 |

| Will you be us  | ing a folder to store the ma | nual? 🗌 Yes 🔲 No                                 |

| What do you t   | hink to the manual presenta  | ation? 🗌 Tidy 🔲 Un-friendly                      |

| Are the explar  | nations understandable?      | ☐ Yes, ☐ Not too bad ☐ Unusable                  |

| -               |                              | nderstand:                                       |

| Are there any   | diagrams which are not cle   | ar?                                              |

|                 |                              | Пол. При п   |

| •               | •                            | ☐ Good ☐ Not too bad ☐ Un-helpfu                 |

|                 | • •                          | nproved, what is it?                             |

|                 |                              |                                                  |

|                 |                              | ed easily using the index and/or the experience: |

|                 |                              |                                                  |

|                 |                              |                                                  |

|                 |                              |                                                  |

| <u>.</u>        |                              |                                                  |

| •               | •                            | oout the Mitsubishi manuals?                     |

|                 |                              |                                                  |

|                 |                              |                                                  |

|                 |                              |                                                  |

| Thank you for   |                              | s questionnaire. We hope you found both          |

|                 | nd this manual easy to use.  |                                                  |

### Guidelines for the safety of the user and protection of the programmable controller (PC)

This manual provides information for the use of the FX family of PCs. The manual has been written to be used by trained and competent personnel. The definition of such a person or persons is as follows;

- a) Any engineer who is responsible for the planning, design and construction of automatic equipment using the product associated with this manual should be of a competent nature, trained and qualified to the local and national standards required to fulfil that role. These engineers should be fully aware of all aspects of safety with regards to automated equipment.

- b) Any commissioning or service engineer must be of a competent nature, trained and qualified to the local and national standards required to fulfil that job. These engineers should also be trained in the use and maintenance of the completed product. This includes being completely familiar with all associated documentation for the said product. All maintenance should be carried out in accordance with established safety practices.

- c) All operators of the completed equipment should be trained to use that product in a safe and co-ordinated manner in compliance to established safety practices. The operators should also be familiar with all documentation which is connected with the actual operation of the completed equipment.

Note: the term 'completed equipment' refers to a third party constructed device which contains or uses the product associated with this manual.

### **Further References:**

For further information regarding the installation and operation of the FX2C please reference the following manuals:

Manual:

### FX Series Programmable Controllers Hardware Manual-

This manual describes the range of available units, their basic features and installation details.

Manual:

### FX Series Programming Manual-

This manual describes the programming features of FX0, FX0N and FX series programmable controllers. All of the FX instructions detailed within this manual are applicable to the FX2C (with the exception of those changes detailed within this supplementary manual).

Manual:

### FX Series Programmable Controller Handy Manual-

This manual describes the programming features of the FX series programmable controllers. All of the FX instructions detailed within this manual are applicable to the FX2C (with the exception of those changes detailed within this supplementary manual).

### 1. Introduction

The following information has been collated in to a small reference guide to the new software features of the FX2C. This introduction brings together all of the attached sheets and catalogs and references them. This should aid the reader in being able to identify where the information is that they require.

These new software features are in addition to a basic program set which was taken from the standard FX PC. If information is required on an existing feature, i.e. one which appears on the FX PC please look for further guidance in either the FX Handy Manual or the new combined FX, FX0N, FX0 Programming Manual.

### 1.1 New FX2C Instructions

| Word Description                | Mnemonic | Function<br>Number | Sheet Reference<br>Number | ☆ Number of pages |

|---------------------------------|----------|--------------------|---------------------------|-------------------|

| ASCII to Hexadecimal Conversion | HEX      | 83                 | SUP 14-☆                  | 2                 |

| Check Code Instruction          | CCD      | 84                 | SUP 15-☆                  | 2                 |

| Float Instruction               | FLT      | 49                 | SUP 3-☆                   | 2                 |

| Hexadecimal to ASCII Conversion | ASCI     | 82                 | SUP 13-☆                  | 2                 |

| PID Control Loop                | PID      | 88                 | SUP 16-☆                  | 5                 |

| Search Instruction              | SER      | 61                 | SUP 21-☆                  | 2                 |

| Serial Communications           | RS       | 80                 | SUP 12-☆                  | 4                 |

| Sort Instruction                | SORT     | 69                 | SUP 22-☆                  | 3                 |

| Square Root Instruction         | SQR      | 48                 | SUP 1-☆                   | 2                 |

### 1.2 Additional/Upgraded FX2C Instructions

| Existing<br>Mnemonic | Word Description                                                    | Sheet Reference<br>Number | ঐ Number<br>of pages |

|----------------------|---------------------------------------------------------------------|---------------------------|----------------------|

| ADD<br>(Fnc 20)      | The Add Instruction Used With The M8023 Float Operation Flag        | SUP 8–☆                   | 3                    |

| BCD<br>(Fnc 18)      | The Decimal To BCD Instruction Used With M8023 Float Operation Flag | SUP 19–☆                  | 2                    |

| BIN<br>(Fnc 19)      | The BCD To Decimal Instruction Used With M8023 Float Operation Flag | SUP 20-☆                  | 2                    |

| DIV<br>(Fnc 23)      | The Divide Instruction Used With The M8023 Float Operation Flag     | SUP 11-☆                  | 3                    |

| FLT<br>(Fnc 49)      | The Float Instruction Used With M8023, The Float Operation Flag     | SUP 4–☆                   | 3                    |

| HKY<br>(Fnc 71)      | The Hexadecimal Key Input Instruction Used For Hexadecimal Input    | SUP 7-☆                   | 3                    |

| HSZ<br>(Fnc 55)      | Zone Compare Instruction With Table Comparison Operation Flag M8130 | SUP 5–☆                   | 3                    |

| HSZ<br>(Fnc 55)      | Zone Compare Instruction Used For Pulse Control With Flag<br>M8132  | SUP 6–☆                   | 3                    |

| MUL<br>(Fnc 22)      | The Multiply Instruction Used With The M8023 Float Operation Flag   | SUP 10-☆                  | 3                    |

| SMOV<br>(Fnc 13)     | The Shift Move Instruction Used With M8168                          | SUP 17-☆                  | 2                    |

| SQR<br>(Fnc 48)      | The Square Root Instruction Used With M8023 Float Operation Flag    | SUP 2–☆                   | 2                    |

| SUB<br>(Fnc 21)      | The Subtract Instruction Used With The M8023 Float Operation Flag   | SUP 9–☆                   | 3                    |

| XCH<br>(Fnc 17)      | The Exchange Instruction Used As A Byte Swap Instruction            | SUP 18-☆                  | <b>2</b>             |

### 1.3 Additional Explanation Sheets

| Word Description                                        | Sheet Reference<br>Number | ☆ Number of pages |

|---------------------------------------------------------|---------------------------|-------------------|

| An Introduction To Number Formats For The FX            | SUP 23-☆                  | 2                 |

| Detailed Explanation Of The Structure Of Floating Point | SUP 24–☆                  | 2                 |

### 1.4 Use of Old Programming Equipment with FX2C PCs

The new instructions in the FX2C cannot be directly accessed using old programming tools. However, certain 'standard' applied instructions can be programmed in conjunction with special auxiliary coils (M coils) to achieve the same 'effective instruction' as the new instructions. The following tables identify which version of peripherals will work directly with all features of the FX2C and which peripherals will need to use the special M coils.

|                                  | PERIPHERALS TABLE |                                                |                                              |  |  |

|----------------------------------|-------------------|------------------------------------------------|----------------------------------------------|--|--|

| Description                      | Model No.         | Old Version requiring use of auxiliary M coils | New version providing complete compatibility |  |  |

| Hand Held Programmer             | FX-10P-E          | V 1.10                                         | V 2.00 ⇔                                     |  |  |

| Hand Held Programmer<br>Cassette | FX-20P-MFXA-E     | V 1.20                                         | V 2.00 ⇔                                     |  |  |

| Programming Software             | FX-PCS/AT-EE      | V 1.01                                         | V 2.00 ≎                                     |  |  |

| Programming Software             | FX-A6GPP-E-KIT    | V 1.00                                         | V 2.00 ⇔                                     |  |  |

|                                  | FX-10DU-E         | V 1.10                                         | V 2.00 ⇔                                     |  |  |

|                                  | FX-20DU-E         | V 1.10                                         | V 2.00 ⇔                                     |  |  |

| Data Access Unit                 | FX-30DU-E         |                                                | V 1.00 ⇔                                     |  |  |

|                                  | FX-40DU-E(S)      | 7                                              | V 1.00 ≎                                     |  |  |

|                                  | FX-40DU-TK-ES     |                                                | V 1.00 ⇔                                     |  |  |

| EXISTING APPLIED INSTRUCTION AND SPECIAL M COIL COMBINATION TO ACHIEVE THE IDENTIFIED NEW FX2C INSTRUCTION |                                                   |                       |                          |      |    |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------|--------------------------|------|----|

| Exi                                                                                                        | Existing FX instruction Mimicked FX2C Instruction |                       |                          |      |    |

| Mnemonic                                                                                                   | FNC Number                                        | Additional<br>M coils | Description Mnemonic FNC |      |    |

| MOV                                                                                                        | 12                                                | M8190                 | Square root              | SQR  | 48 |

| MOV                                                                                                        | 12                                                | M8191                 | Float                    | FLT  | 49 |

| RAMP                                                                                                       | 67                                                | M8193                 | Data search              | SER  | 61 |

| RAMP                                                                                                       | 67                                                | M8194                 | RS232 Instruction        | RS   | 80 |

| FMOV                                                                                                       | 16                                                | M8196                 | HEX to ASCII conversion  | ASCI | 82 |

| FMOV                                                                                                       | 16                                                | M8196                 | ACII to HEX conversion   | HEX  | 83 |

| FMOV                                                                                                       | 16                                                | M8195                 | Sum check                | CCD  | 84 |

### 1.5 High Speed Instructions

One of the major new features of the FX2C is the enhanced processing of both basic and applied instructions. A full listing of available instructions for each of the program—mable controllers in the FX series and their associated execution times can be found at the back of this supplementary manual (pages ET-1 to 10).

Under the FX2C listings, where applicable, the execution times for the second (2nd FNC) functions, i.e those 'standard applied instructions' which are modified by an additional special Mcoil to perform one of the new FX2C functions, have also been listed.

### 1.6 Functions with Minor Upgrades

| Functions                       | Description of Change                                                                              | Remark                              |

|---------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------|

| El                              | Now activates a pulse catch on the high speed inputs when not used for another high speed purpose. | Catch signaled with M8170 to M8175. |

| BMOV                            | Can now read and WRITE to file registers.                                                          | RAM file registers also possible.   |

| HSCS                            | Now possible to activate an interrupt.                                                             | Uses I010 to I060 for output.       |

| PLSY                            | Output pulses counted in a double word device.                                                     | Uses D8137,D8136                    |

| (D)FMOV,<br>(D)MEAN,<br>(D)ABSD | Double Word instructions are now possible.                                                         |                                     |

| DSW,<br>SEGL, PR                | Up to 2 instructions can be programmed in one program at the same time.                            |                                     |

### 1.7 New RUN/STOP Switch

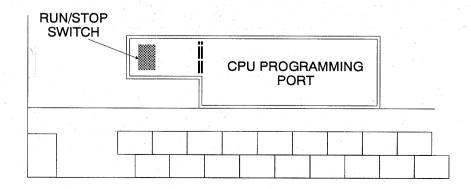

The FX2C has a built in RUN/STOP switch (for further information see the appropriate hardware manual). Certain models of the Japanese specification FX2 series units also have the same programming specification and the RUN/STOP switch as the FX2C. The location of the RUN/STOP switch for the Japanese specification units is as shown in the diagram below. The switch operates in parallel with the RUN input terminal.

# AN INTRODUCTION TO THE SQUARE ROOT INSTRUCTION (SQR, FNC 48)

### Introduction

The FX PC family has a powerful set of applied instructions as well as the commonly used basic instructions. The applied instructions are versatile additions to the basic set and provide control over internal PC operations and external I/O. There are 10 groups of applied instructions, each with a different area of application, eg. arithmetic and logical operations.

Applied instructions 40 to 49 are concerned with the conversion between different data formats within the PC and are grouped under the heading of Data operations.

This group includes the Square Root instruction (SQR, FNC 48). This performs the mathematical operation

$$y = \sqrt{x}$$

on the given data and returns a truncated whole number for the answer.

### The Square Root Instruction

The Square Root instruction has three parameters:

- a) the SQR statement itself

- b) the specification of the operand i.e. the device or value on which square root is performed.

- c) the specification of the result data's destination, i.e. where the result is to be put.

Shown below is the typical appearance of the SQR instruction in a ladder program, while the following table shows the same piece of ladder logic written in instruction format.

|             | PARAMETERS |     |      |

|-------------|------------|-----|------|

|             |            |     |      |

| T47         | ´ a        | b   | c \  |

| <del></del> | SQR        | D75 | D129 |

|             |            |     |      |

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |     |

|---------------------|---------------------|---|-----|

| 0                   | LD                  | Т | 47  |

| 1                   | SQR                 |   | 48  |

|                     |                     | D | 75  |

|                     |                     | D | 129 |

It can be seen from the ladder program that when timer T47 turns ON, the square root instruction executes. It reads the contents of D75, calculates the square root and stores it in the data register D129. The following section looks at each parameter in greater detail:

#### Parameter a) - The SQR statement

The SQR statement can take four different forms:

- SQR: The standard form of the instruction, taking 5 steps of program. While the SQR instruction is operating the result is continually calculated.

- II) SQRP: The "P" suffix shows that SQR is being used in its PULSE format. The instruction will only calculate the result once when it is turned ON. SQRP also takes 5 program steps.

- III) DSQR: This is similar to SQR, but the "D" prefix means DOUBLE word is used in the calculation for both the operand and the result, ie. 32 bits, equivalent to two consecutive data registers. DSQR takes 9 steps of program.

- IV) DSQRP: This combines the DOUBLE word format with the PULSE operation to give a SQR instruction which calculates the square root of 32 bits of data when first turned ON. DSQRP takes 9 program steps.

### Parameter b) - Operand

This identifies the location of the operand for the square root calculation. The data is either 16 or 32 bits (SQR, DSQR) and can be either a constant (K,H) or a data register (D). If the value is negative then the SQR instruction will generate an execution error.

#### Parameter c) - Destination

This is where the result of the calculation is placed. The data is always stored in a data register (D) as either 16 or 32 bits. The result is rounded down to the nearest whole number by ignoring the fractional part.

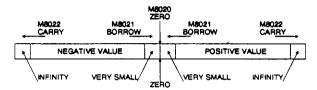

M8020 zero flag operates if the result is zero.

M8021 borrow flag operates if the result is rounded.

# AN INTRODUCTION TO THE SQUARE ROOT INSTRUCTION (SQR, FNC 48)

### Example Use of the Square Root Instruction

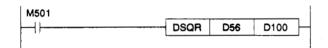

The diagram below shows the square root instruction being used to calculate the square root of the current contents of data register pair D57 and D56 and store the result in the data register pair D101 and D100. This occurs when the auxilliary relay M501 turns on.

The table below shows some example results of the square root instruction. Note that all values are rounded down to the nearest whole number. If the true root value is needed then it is recommended that the floating point version of the SQR instruction is used, see SUP 2.

| OPERAND          | ROOT    | SQR RESULT |

|------------------|---------|------------|

| 25               | 5.0     | 5          |

| 60               | 7.746   | 7          |

| <del>-2</del> 36 | 15.36 i | ERROR      |

| 147              | 12.124  | 12         |

### THE SQUARE ROOT INSTRUCTION (SQR, FNC 48) USED WITH M8023 FLOAT OPERATION FLAG

### Introduction

The FX PC family has a powerful set of applied instructions as well as the commonly used basic instructions. The applied instructions are versatile additions to the basic set and provide control over internal PC operations and external I/O. There are 10 groups of applied instructions, each with a different area of application, eg. arithmetic and logical operations.

Applied instructions 40 to 49 are concerned with the conversion between different data formats within the PC and are grouped under the heading of Data operations.

This group includes the square root instruction (SQR, FNC 18). When used in conjunction with the float operation flag M8023 the SQR instruction calculate the square root of data from a floating point number or constant and gives the result as a floating point number.

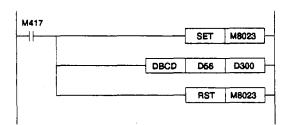

### The SQR Instruction with M8023

This form of the SQR instruction has three parts:

Part 1: Set M8023

a) setting the floating point operation flag.

Part 2: The SQR instruction (three parameters)

- b) the SQR statement itself.

- c) the specification of the operand i.e. the number which is to be square rooted.

- d) the specification of the destination data i.e. to where the result of the calculation is to be written.

Part 3: Reset M8023

e) resetting the floating point operation flag.

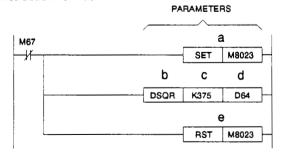

Shown below is this format of the SQR instruction as a ladder diagram showing each of these features. The following table shows the same program written in instruction format.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |      |  |

|---------------------|---------------------|---|------|--|

| 0                   | LDI                 | М | 67   |  |

| 1                   | SET                 | М | 8023 |  |

| 3                   | DSQR                |   | 48   |  |

|                     |                     | K | 375  |  |

|                     |                     | D | 64   |  |

| 12                  | RST                 | М | 8023 |  |

Looking at the ladder diagram we can see that when the auxiliary relay M67 is turned OFF, first the float operation flag is set to ON, then the SQR instruction executes. This results in the square root of the constant K375 being calculated as a floating point number. This value is then written to the data register pair D65 and D64. Finally the float operation flag is reset.

### Parameter a) - Setting the float flag

The Float Operation flag M8023 must be SET. This flag changes the function of the SQR instruction and other math functions to operate on floating point numbers.

### Parameter b) - The SQR statement

The SQR statement can only be DOUBLE word when used with the float operations flag:

- DSQR: The basic format for this use of the SQR instruction, taking 9 steps of program memory. While the instruction is ON it continues to execute. The "D" prefix indicates DOUBLE word operation, i.e. two consecutive data registers (32 bits).

- DSQRP: This is the PULSE format of the DSQR instruction. The instruction will execute once when it is first turned ON (i.e. rising edge execution) and operates on 32 bits of data.

#### Parameter c) - Source Data

This identifies the location of the value to be square rooted. The data can be either a constant (K,H) or held in data registers (D) and must be a floating point format number. Constants are converted to floating point automatically. If the number is a negative value then an execution error will occur.

### THE SQUARE ROOT INSTRUCTION (SQR, FNC 48) USED WITH M8023 FLOAT OPERATION FLAG

### Parameter d) - Destination Data

This identifies the location where the result of the calculation is to be written. The data will be written in floating point and the device must be a data register (D) pair.

The zero flag M8020 will operate if the result is zero.

### Parameter e) - Resetting the float flag

The Float Operation flag must be RESET to allow further functions to operate as normal. The flag can be left on if further operations requiring floating point calculations are needed. However, it is recommended that once all floating point functions are completed this flag should be switched off using RST.

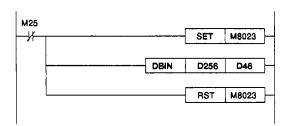

### **Example Use of the SQR Instruction**

The diagram below shows the SQR instruction calculating the square root of the data register pair D257 and D256. The result in floating point format is written to data register pair D47 and D46.

| C56 |      | SET  | M8023 |

|-----|------|------|-------|

|     | DSQR | D256 | D46   |

|     |      | RST  | M8023 |

|     |      |      |       |

| OPERAND                   | ROOT  | DSQR RESULT             |

|---------------------------|-------|-------------------------|

| 2.5 × 10 <sup>5</sup>     | 500.0 | 5.00 × 10 <sup>2</sup>  |

| 4.9 × 10 <sup>-3</sup>    | 0.07  | 7.00 × 10 <sup>-2</sup> |

| K15129                    | 123   | 1.23 × 10 <sup>2</sup>  |

| - 4.096 × 10 <sup>3</sup> | 64 i  | ERROR                   |

The table above shows some example results of the SQR instruction being used with the M8023 float operation flag.

# AN INTRODUCTION TO THE FLOAT INSTRUCTION (FLT, FNC 49)

### Introduction

The FX PC family instruction set is divided into two groups: basic and applied instructions. The applied instructions are powerful supplements to the basic set of PC instructions and are used to provide control over internal PC operations and external I/O. They are split into 10 groups, each group with a different emphasis, eq. arithmetic and logical operations.

Applied instructions 40 to 49 are concerned with the conversion between different data formats within the PC and are grouped under the heading of Data operations.

This group includes the Float instruction (FLT, FNC 49). This provides the facility to convert data in the PC from integer format to data in floating point format (float).

### The Float Instruction

The Float instruction has three parameters:

- a) the FLT statement itself

- b) the specification for the Source Data, ie. where the data in decimal format is taken from.

- c) the specification for the converted data's Destination, i.e. where the converted data is to be put.

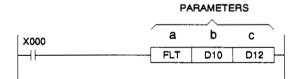

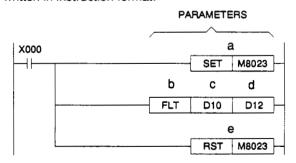

Shown below in Figure1 is the typical appearance of a Float instruction in a ladder program. While Figure 2 shows the same piece of ladder logic written in instruction format.

Figure 1: The Float instruction in ladder format.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |     |

|---------------------|---------------------|---|-----|

| 0                   | LD                  | X | 000 |

| 1                   | FLT                 |   | 49  |

|                     |                     | D | 10  |

|                     |                     | D | 12  |

Figure 2: The Float instruction in instruction format.

Following Figure 1, when input X000 is turned on, the effect of the Float instruction is to read the contents of D10, convert this value in to a float value and put it into the Data Register pair D13 and D12. The following section explains each parameter in greater detail:

#### Parameter a) - The FLT statement

The FLT statement can take four different forms:

- FLT: The standard form of the instruction, taking 5 steps of program. In the example shown in Figure 1, while X000 is turned on, the FLT instruction will operate.

- II) FLTP: The "P" suffix shows that FLT is being used in its PULSE format. The instruction will only operate when X000 provides a rising edge signal as it turns on. FLTP also takes 5 program steps.

- III) DFLT: This is similar to FLT, but the "D" prefix indicates the instruction is converting a DOUBLE word, ie. 32 bits, equivalent to two consecutive data registers. DFLT takes 9 steps of program.

- IV) DFLTP: This combines the DOUBLE word format with the PULSE operation to give a FLT instruction which will convert 32 bits of data from the Source to the Destination when given a rising edge on its associated bit device, X000 in this case. DFLTP takes 9 program steps.

### Parameter b) - Source Data

This identifies the location of the Source Data to be converted. The data is either 16 or 32 bits (FLT, DFLT) and must be held in a data register (D).

### Parameter c) - Destination

This is where the converted Source Data is placed. The data is always stored in float format in a Data Registers (D) pair.

# AN INTRODUCTION TO THE FLOAT INSTRUCTION (FLT, FNC 49)

### **Example Use of the Float Instruction**

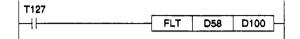

Figure 3: Example of the FLT instruction.

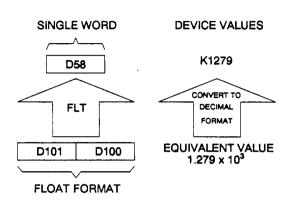

Figure 3 shows the Float instruction being used to convert the current contents of data register D58 and store the result in the data register pair D101 and D100 as a floating point number. This occurs when the timer contact T127 turns on.

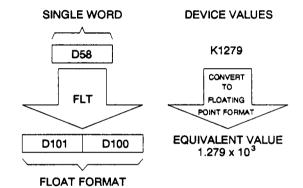

Figure 4 illustrates the operation of this instruction giving an example of the contents of the data registers.

Figure 4: Operation of the FLT instruction.

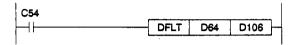

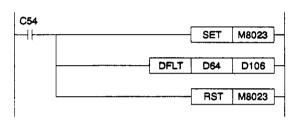

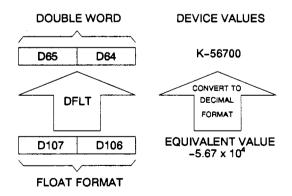

Figure 5: Example of the DFLT instruction.

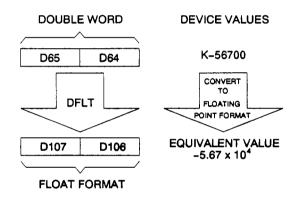

Figure 5 shows the Float instruction being used to convert the current contents of data registers D64 and D65 as a double word and store the result in the data register pair D107 and D106 in float format. This occurs when the counter contact C54 turns on.

Figure 6 illustrates the operation of this instruction giving an example of the contents of the data registers.

Figure 6: Operation of the DFLT instruction.

### THE FLOAT INSTRUCTION (FLT, FNC 49) USED WITH M8023, FLOAT OPERATION FLAG

### Introduction

The FX PC family instruction set is divided into two groups: basic and applied instructions. The applied instructions are powerful supplements to the basic set of PC instructions and are used to provide control over internal PC operations and external I/O. They are split into 10 groups, each group with a different emphasis, eg. arithmetic and logical operations.

Applied instructions 40 to 49 are concerned with the conversion between different data formats within the PC and are grouped under the heading of Data operations.

This group includes the Float instruction (FLT, FNC 49). When used in conjunction with the Float Operation flag this provides the facility to convert data in the PC from floating point format (float) to data in decimal format.

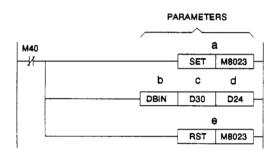

### The Float Instruction

The Float instruction has three parts:

Part 1: Set M8023

a) setting the floating point operation flag.

Part 2: the float instruction (three parameters)

b) the Float in statement itself

- c) the specification for the decimal data location, ie. where the data in decimal format is placed.

- d) the specification for the floating point data location, ie. where the floating point data to be converted is taken from.

Part 3: Reset M8023

e) resetting the floating point operation flag.

Shown below in Figure 1 is the format of a Float instruction with the float flag, in a ladder program. While Figure 2 shows the same piece of ladder logic written in instruction format.

Figure 1: The Float instruction in ladder format.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |      |

|---------------------|---------------------|---|------|

| 0                   | LD                  | Х | 000  |

| 1                   | SET                 | М | 8023 |

| 3                   | FLT                 |   | 49   |

|                     |                     | D | 10   |

|                     |                     | D | 12   |

| 8                   | RST                 | М | 8023 |

Figure 2: The Float instruction in instruction format.

Following Figure 1, when input X000 is turned ON, the float operation flag is set ON, the effect of the Float instruction is to read the contents of the data register pair D13 and D12, convert this float value into a decimal value and put it into data register D10. The float operation flag is then reset. The following section explains each parameter in greater detail:

### Parameter a) - Setting the float flag

The Float Operation flag M8023 must be SET. This flag changes the function of the FLT instruction and math functions to operate on floating point numbers.

### Parameter b) - The FLT statement

The FLT statement can take four different forms:

- FLT: The standard form of the instruction, taking 5 steps of program. In the example shown in Figure 1, while X000 is turned on, the FLT instruction will operate converting the float value into decimal.

- II) FLTP: The "P" suffix shows that FLT is being used in its PULSE format. The instruction will only operate when X000 provides a rising edge signal as it turns on. FLTP also takes 5 program steps.

- III) DFLT: This is similar to FLT, but the "D" prefix indicates the instruction converts to a DOUBLE word, ie. 32 bits, equivalent to two consecutive data registers. DFLT takes 9 steps of program.

# THE FLOAT INSTRUCTION (FLT, FNC 49) USED WITH M8023, FLOAT OPERATION FLAG

IV) DFLTP: This combines the DOUBLE word format with the PULSE operation to give a FLT instruction which will convert to 32 bit data when given a rising edge on its associated bit device, X000 in this case. DFLTP takes 9 program steps.

### Parameter c) - Decimal Data

This identifies the location of the decimal value after the conversion. The data is either 16 or 32 bits (FLT, DFLT) and must be held in a data register (D).

### Parameter d) - Float Data

This is where the floating point value is taken from before the conversion to decimal. The data is always stored in float format in a Data Registers (D) pair.

### Parameter e) - Reset M8023

The Float Operation flag M8023 must be RESET to allow further functions to operate as normal. The flag can be left on if further operations requiring floating point calculations are needed. However it is recommended that once all floating point functions are completed this flag should be switched off using RST.

### **Example Use of the Float Instruction**

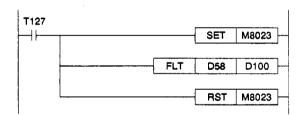

Figure 3: Example of the FLT instruction.

Figure 3 shows the Float instruction being used to convert the current contents of data register pair D101 and D100 as a float format number and store the result in data register D58 as a decimal value. This occurs when the timer contact T127 turns on.

Figure 4 illustrates the operation of this instruction giving an example of the contents of the data registers.

Figure 4: Operation of the FLT instruction.

Figure 5: Example of the DFLT instruction.

Figure 5 shows the Float instruction being used to convert the current contents of the data register pair D107 and D106 as a float format number and store the result in data registers D64 and D65 as a double word in decimal. This occurs when the timer contact C54 turns on.

Figure 6 illustrates the operation of this instruction giving an example of the contents of the data registers.

Figure 6: Operation of the DFLT instruction.

# ZONE COMPARE INSTRUCTION (HSZ, FNC 55) WITH TABLE COMPARISON OPERATION FLAG M8130

### Introduction

The FX PC family instruction set is divided into two groups: basic and applied instructions. The applied instructions are powerful supplements to the basic set of PC instructions and are used to provide control over internal PC operations and external I/O. They are split into 10 groups, each group with a different emphasis, eg. arithmetic and logic.

Applied instructions 50 to 59 are all high speed instructions designed to perform independently of the program scan. This gives the group its name; High Speed instructions.

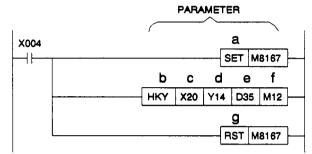

Included in the High Speed instructions is the high speed zone compare instruction (DHSZ, FNC 55). This instruction is used to monitor the value of a high speed counter (HSC). When the destination is set to special auxiliary relay M8130 the data stored in a table is compared and an output device specified in the table is changed accordingly. The table defines sequential DHSCS (FNC 53) and DHSCR (FNC 54) operations for the same counter.

### The High Speed Zone Compare Instruction

The DHSZ instruction has 5 parameters:

- a) the DHSZ statement itself

- b) the table head address; the first data register of the comparison table.

- c) the table length; the number of items in the table.

- d) the test device; the high speed counter to be monitored.

- e) the destination device; set to M8130 for this special function.

Shown below, in both ladder and instruction format, is the basic appearance of this form of the DHSZ instruction.

PARAMETERS

| X010        | a    | b    | c  | d    | е     |

|-------------|------|------|----|------|-------|

| <del></del> | DHSZ | D200 | K5 | C251 | M8130 |

|             |      |      |    |      |       |

Figure 1: Example ladder for DHSZ instruction.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |      |

|---------------------|---------------------|---|------|

| 0                   | LD                  | X | 10   |

| 1                   | DHSZ                |   | 55   |

|                     |                     | D | 200  |

|                     |                     | K | 5    |

|                     |                     | С | 251  |

|                     |                     | М | 8130 |

Figure 2: Example of DHSZ in instruction format

In the example given, each time the high speed counter C251 counts one pulse, the DHSZ instruction tests C251's current value with the value of the table entry; starting at D200 and having 5 entries. If the values match then the specified output is either set or reset and the comparison moves on to the next item in the table. When all items in the table have been matched (five in this example;K5) the table counter cycles back to the first item.

The following sections explain each parameter in more detail.

#### Parameter a) - The HSZ statement

This instruction has two forms but only one can be used.

- HSZ: THIS FORMAT WILL NOT WORK.

Although it is possible to enter the instruction in this format the comparison will not give the expected results.

DO NOT use this format.

- II) DHSZ: The "D" prefix indicates that this is the DOUBLE word format of the instruction. Only this format is valid because the instruction must be used with a high speed counter (all 32 bit). All word devices specified will be double word, i.e. 2 data registers or 32 bits of data will be used in the comparison. In this format the instruction takes 17 steps of program memory.

### ZONE COMPARE INSTRUCTION (HSZ, FNC 55) WITH TABLE COMPARISON OPERATION FLAG M8130

### Parameter b) - The table head address

This data register (D) specifies the first data register of the control table. The control table defines the values to be tested and the affect to the output when a match is made.

### Parameter c) - The table length

The number of entries in the table is specified with a constant value (K,H). A maximum of 128 entries is allowed. A total of 4 data registers are used per entry. The following data must be defined for each entry in the table:

- The comparison value (Double Word).

- The output affected (Hexadecimal).

- The Set or Reset action.

|              | ENTRY<br>No. | COMPARISON<br>VALUE | OUTPUT<br>DEVICE           | SET/<br>RESET |  |

|--------------|--------------|---------------------|----------------------------|---------------|--|

|              | 110.         | LOWER,UPPER         |                            |               |  |

|              | 0            | D200,D201<br>K123   | <b>D2</b> 02<br>H10 (=Y10) | D203<br>K1    |  |

| <del>δ</del> | 1            | D204,D205<br>K234   | D206<br>H10                | D207<br>K0    |  |

| Length       | 2            | D208,D209<br>K345   | D210<br>H23 (=Y23)         | D211<br>K1    |  |

| _            | 3            | D212,D213<br>K456   | D214<br>H23                | D215<br>K0    |  |

|              | 4            | D216,D217<br>K567   | D218<br>H23                | D219<br>K1    |  |

Figure 3: Example control table; Start address D200, length K5.

The comparison value is a double word device using two consecutive data registers in the table.

Following this is the output device; specified in hexadecimal.

The last item in each entry indicates setting or resetting of the output device; K1 —set, K0 —reset.

### Parameter d) - The test device

This is the high speed counter that is tested by the DHSZ instruction. Each time the counter counts, its new value is checked against the current entry in the table. When a match is made the specified output is either set or reset and the table current entry is move on to the next. Only the High Speed Counters can be used with this function; (C235 to C255).

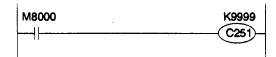

Note: The correct HSC circuit must also be programmed.

Figure 4: Minimum program required for HSC.

#### Parameter e) - The destination device

This parameter normally specifies the output devices to be set for the comparison. In this case the specification of special auxiliary relay M8130 indicates that a table is to be used to define the comparison values and the output devices affected.

There can only be 1 DHSZ instruction using the flag M8130 at any one time; i.e. only one switched on.

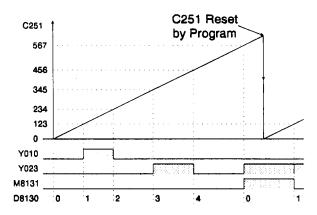

### **High Speed Table Comparison Operation**

Figure 5: Operation of the outputs and the table counter D8130.

When M8130 is used with DHSZ special data register D8130 is defined as the current entry counter. As each comparison value is matched D8130 increments to the next entry number to be compared. Once all entries in the table have been matched the table counter returns to the beginning and the operation complete flag M8131 turns on.

If the counter is reset (by program or external pulse) and counts up to the first comparison value again then the operation complete flag M8131 is reset.

If the DHSZ instruction is switched off then D8130 is reset to 0 and M8131 is reset to off. All the output devices controlled by DHSZ will be left in their last state.

**SUP 5-3**

# ZONE COMPARE INSTRUCTION (HSZ, FNC 55) WITH TABLE COMPARISON OPERATION FLAG M8130

### **Important Notes**

Only 6 high speed comparison functions can be active at any one time. High speed comparisons include DHSCS, DHSCR and all forms of DHSZ. Any number may be in the program but only 6 can be switched on.

When a high speed comparison is first switched on it will not be active until after the first END is executed. This is to allow the FX to initialize its internal comparison table. This will only be a problem if the high speed counter current value is close to the compare value at the time the instruction is switched on.

This instruction is interrupt processed and only operates when a signal is received at the HSC input. Therefore, changing the HSC current value or resetting the HSC from within the FX program will not be recognized until the next pulse is received at the HSC input.

The comparison values are checked in a sequential order. Take care to ensure the comparison values always increment or decrement, following the HSC operation.

# ZONE COMPARE INSTRUCTION (HSZ, FNC 55) USED FOR PULSE CONTROL WITH FLAG M8132

### Introduction

The FX PC family instruction set is divided into two groups: basic and applied instructions. The applied instructions are powerful supplements to the basic set of PC instructions and are used to provide control over internal PC operations and external I/O. They are split into 10 groups, each group with a different emphasis, eg. arithmetic and logic.

Applied instructions 50 to 59 are all high speed instructions designed to perform independently of the program scan. This gives the group its name; High Speed instructions.

Included in the High Speed instructions is the high speed zone compare instruction (DHSZ, FNC 55). This instruction is used to monitor the value of a high speed counter (HSC). When the destination is set to special auxiliary relay M8132 the data stored in a table is compared and on a match the frequency defined in the table is used to control the pulse output frequency of the PLSY (FNC 57) instruction.

### The High Speed Pulse Control Instruction

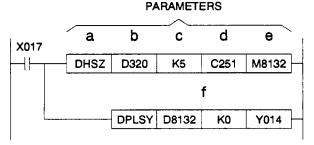

The DHSZ instruction in this format has 6 parameters:

- a) the DHSZ statement itself

- b) the table head address; the first data register of the comparison table.

- c) the table length; the number of items in the table.

- d) the test device; the high speed counter to be monitored.

- e) the destination device; set to M8132 for this special function.

- f) the DPLSY instruction; D8132 is used as the frequency control register.

Shown below, in both ladder and instruction format, is the basic appearance of this form of the DHSZ instruction.

Figure 1: Example ladder for DHSZ instruction.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |            |      |

|---------------------|---------------------|------------|------|

| 0                   | LD                  | X          | 10   |

| 1                   | DHSZ                |            | 55   |

|                     |                     | <b>D</b> . | 320  |

|                     |                     | K          | 5    |

|                     |                     | С          | 251  |

|                     |                     | M          | 8132 |

| 18                  | DPLSY               |            | 57   |

|                     |                     | D          | 8132 |

|                     |                     | K          | 0    |

Figure 2: Example of DHSZ in instruction format

In the example given, the DPLSY frequency is set to the first value in the table. Each time the high speed counter C251 counts one pulse, the DHSZ instruction tests C251's current value with the current value in the table; starting at D200 and having 5 entries.

If the values match then the comparison moves on to the next item in the table and the DPLSY frequency is set from this new entry until the new entry's comparison value is reached. When all items in the table have been matched (five in this example) the table counter cycles back to the first item.

The following sections explain each parameter in more detail.

#### Parameter a) - The HSZ statement

This instruction has two forms but only one can be used.

- HSZ: THIS FORMAT WILL NOT WORK.

Although it is possible to enter the instruction in this format the comparison will not give the expected results.

DO NOT use this format.

- II) DHSZ: The "D" prefix indicates that this is the DOUBLE word format of the instruction. Only this format is valid because the instruction must be used with a high speed counter (all 32 bit). All word devices specified will be double word, i.e. 2 data registers or 32 bits of data will be used in the comparison. This format of the instruction takes 17 program steps.

### ZONE COMPARE INSTRUCTION (HSZ, FNC 55) USED FOR PULSE CONTROL WITH FLAG M8132

#### Parameter b) - The table head address

This data register (D) specifies the first data register of the control table. The control table defines the values to be tested and the affect when a match is made.

#### Parameter c) - The table length

The number of entries in the table is specified with a constant value (K,H); a maximum of 128 entries is allowed. A total of 4 data registers are used per entry. The following data must be defined for each entry in the table:

- The comparison value (Double Word).

- The output affected (Double Word).

|   | ENTRY<br>No. | COMPARISON<br>VALUE | OUTPUT<br>FREQUENCY<br>(0 to 1000Hz) |

|---|--------------|---------------------|--------------------------------------|

|   |              | LOWER, UPPER        | LOWER, UPPER                         |

|   | 0            | D320, D321<br>K20   | D322, D323<br>K300                   |

|   | 1            | D324, D325<br>K600  | D326, D327<br>K500                   |

| , | 2            | D328, D329<br>K700  | D330, D331<br>K200                   |

|   | 3            | D332, D333<br>K800  | D334, D335<br>K100                   |

| 1 |              |                     |                                      |

Figure 3: Example control table; Start address D320, length K5.

The comparison value is a double word device using two consecutive data registers in the table.

Following this is the pulse output frequency; this is the frequency that is set until the HSC matches the comparison value.

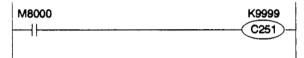

#### Parameter d) - The test device

This is the high speed counter that is tested by the DHSZ instruction. Each time the counter counts, its new value is checked against the current entry in the table. When a match is made the table current entry is moved on to the next and the PLSY frequency is set from the new table entry using D8132. Only the High Speed Counters can be used with this function; (C235 to C255).

Note: The correct HSC circuit must also be programmed.

Figure 4: Minimum program required for HSC C251

### Parameter e) - The destination device

This parameter normally specifies the output devices to be set for the comparison. In this case the specification of special auxiliary relay M8132 indicates that a table is to be used to define the comparison values and set the pulse frequencies.

There can only be 1 DHSZ instruction using the flag M8132 at any one time; i.e. only one switched on.

### **High Speed Pulse Control Operation**

Figure 5: Graph showing the frequency set as the HSC reaches each value in the table.

When M8131 is used with DHSZ special data register D8131 is defined as the current entry counter. As each comparison value is matched D8131 increments to the next entry number to be compared.

The special data register D8132 is set to the frequency of the current entry. When this is used with the PLSY instruction the pulse output can be controlled.

To help monitor the process the data register pair D8134 and D8135 store the value of the current comparison value.

When the final comparison is made the completion flag M8133 is set on and the table counter cycles back to the first entry.

When the DHSZ instruction is switched off all values are reset; including the frequency output.

# ZONE COMPARE INSTRUCTION (HSZ, FNC 55) USED FOR PULSE CONTROL WITH FLAG M8132

### **Important Notes**

Only 6 high speed comparison functions can be active at any one time. High speed comparisons include DHSCS, DHSCR and all forms of DHSZ. Any number may be in the program but only 6 can be switched on.

When a high speed comparison is first switched on it will not be active until after the first END is executed. This is to allow the FX to initialize its internal comparison table. This will only be a problem if the high speed counter current value is close to the compare value at the time the instruction is switched on.

This instruction is interrupt processed and only operates when a signal is received at the HSC input. Therefore, changing the HSC current value or resetting the HSC from within the FX program will not be recognized until the next pulse is received at the HSC input.

The comparison values are checked in a sequential order. Take care to ensure the comparison values always increment or decrement, following the HSC operation.

Because frequency output is commonly used to control active machinery it is recommended that the final entry in the table is set to K0,K0. This will ensure that the pulse output is stopped and the table counter will not return to the beginning. If this is done then monitoring special register pair D8134,D8134 for a value of K0 will indicate the end of the table.

# THE HEXADECIMAL KEY INPUT INSTRUCTION (HKY, FNC 71) USED FOR HEXADECIMAL INPUT

### Introduction

The FX PC family instruction set is divided into two groups: basic and applied instructions. The applied instructions are powerful supplements to the basic set of PC instructions and are used to provide control over internal PC operations and external I/O. They are separated into 10 groups, each group having a different emphasis, eg. arithmetic and logic.

Applied instructions 70 to 79 are grouped together under the heading of external Input/Output devices and provide facilities to pass information to and from external equipment and peripherals.

Included in these I/O instructions is the Hexadecimal KeY instruction (HKY, FNC 71). This instruction uses inputs and outputs in a multiplexing operations to read the key presses from a 16 key keypad. The number keys when pressed are recorded in sequence in a data register as a hexadecimal value and the six alpha keys, as well as being data inputs, signal a bit device to be set on for use as a special function key.

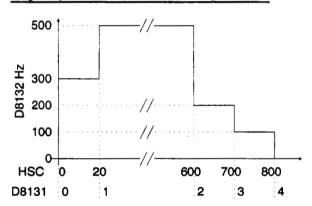

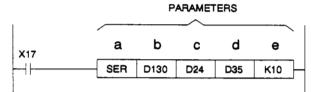

### The Hexadecimal Key Input

The HKY input instruction has seven parameters:

- a) setting the Hexadecimal mode flag.

- b) the HKY statement itself.

- the input head address; the first of the inputs to which the key signals are connected.

- the output head address; the first of the outputs to which the multiplexing control signals are connected.

- the numerical storage register; the data register(s) where the entered number is placed.

- f) the function key head address; the first of the bit devices used for the function key operation.

- g) resetting the hexadecimal mode flag.

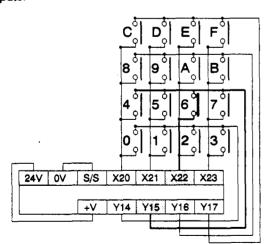

Shown above is the typical appearance of an HKY instruction in both ladder and instruction format.

Figure 1: Ladder program of the basic format for the HKY instruction.

| PROGRAM<br>STEP No. | INSTRUCTION PROGRAM |   |      |

|---------------------|---------------------|---|------|

| 0                   | LD                  | X | 4    |

| 1                   | SET                 | М | 8167 |

| 3                   | HKY                 |   | 71   |

|                     |                     | X | 20   |

|                     |                     | Y | 14   |

|                     |                     | D | 35   |

|                     |                     | М | 12   |

| 12                  | RST                 | М | 8167 |

Figure 2: Instruction program of the basic format for the HKY instruction.

The above figures show the typical appearance of the hexadecimal keypad input function in instruction and ladder program formats, When executed using input X4 this program sets each of the outputs Y14 to Y17 on in turn and reads the inputs X20 to X23 to test for a key press. Either the number pressed (0 to 9) is shifted into the data register D35 or the appropriate function flag M12 to M18 is set for the alpha key pressed (A to F). The following section explains each parameter in greater detail.

### THE HEXADECIMAL KEY INPUT INSTRUCTION (HKY, FNC 71) USED FOR HEXADECIMAL INPUT

### Parameter a) - Setting Hexadecimal Mode

The HKY hexadecimal mode key is needed to swithc the operation of the HKY instruction to interpret all 16 key as hexadecimal data input.

### Parameter b) - The HKY statement

The HKY statement can take two different forms:

- HKY: The standard form of the instruction, taking 9 steps of program. When activated the function operates continuously using the other parameters given.

- II) DHKY: This is similar to HKY, but the "D" prefix indicates the instruction stores the number in a DOUBLE word of data, ie. 32 bits, equivalent to two data registers.

### Parameter c) - Input Head Address

This identifies the first of the four inputs used to read the data entered using the keypad. Only an input (X) can be specified for this parameter. A total of four consecutive inputs will be allocated.

### Parameter d) - Output Head Address

This identifies the first of the four outputs used to scan the keys pressed on the keypad. Combined with the inputs, a grid is made and the outputs are sequential set and reset to trap a closed switch at one of the inputs.

Figure 3: The Inputs and the outputs are connected to form the hexadecimal keypad.

When output Y15 is on key 6 is detected at input X22.

Each of the outputs are switched on in turn, activating one of the rows of keys. If a key is pressed then the corresponding input is also turned on and the key press can be identified. Only outputs (Y) can be specified for this parameter. A total of four outputs will be allocated.

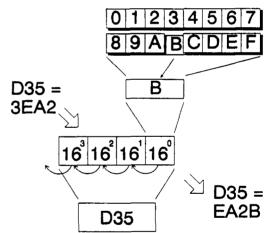

### Parameter e) - Numerical Storage Register

This identifies the data register (first of a pair if DOU-BLE word is used) where the hexadecimal value entered on the keypad is stored. As each key is pressed the numbers 0 to 9 and the letters A to F are recorded in this data register and a number up to FFFFHEX (FFFFFFHEX for DOUBLE word) can be entered.

When a key is pressed the contents of the data register are shifted one place to the left (multiplied by 10HEX) and the new number is entered in the least significant digit (units) position. The following diagram shows this operation.

Figure 4: Number Key entry into the storage data register.

The number will overflow if the number of digits exceeds the maximum of 4 (8 if DOUBLE word).

### THE HEXADECIMAL KEY INPUT INSTRUCTION (HKY, FNC 71) USED FOR HEXADECIMAL INPUT

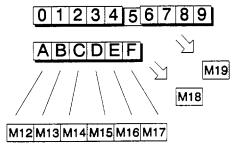

### Parameter f) - Function Key Head Address

This identifies the first of a group of 8 bit device used to record the function key presses and control signals.

Figure 5: Function keys and key press flags.

M15: D has been pressed.

M19: A number (5) is now being pressed.

The first six correspond to the alpha keys pressed, the next is on while an alpha key is pressed and the last is on while a number key is pressed.

If a function key flag is already set and a different key is pressed the first flag is reset and the new key pressed identified by its function flag being set on.

After any key press has been sensed, the execution complete flag M8029 is set on.

### Operation Speed

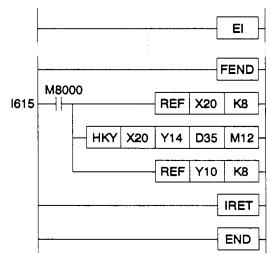

The HKY instruction is processed during each execution of the ladder program. This means that one full reading of the key pad will take 8 program scan to execute (i.e. one complete ON/OFF cycle for each output). After each output is set ON the inputs need to be processed to obtain the key signal. Therefore the response time of the HKY instruction is dependant upon the execution speed of the program and the limiting speed is determined by the response time of the inputs.

For fast programs it is possible that the inputs might not respond in time with the outputs because of input filtering delays. This can be controlled using constant scan mode and setting the scan time to more than 20ms (input filters are approx. 10ms ON/OFF).

If the normal scan time proves to be too slow then use of a timer interrupt is possible. When a timer interrupt routine is used it is necessary to refresh the inputs before execution and the outputs after execution of the HKY instruction. This is done using the REF instruction.

Note: It is also necessary to set the interrupt timer to be a little more than the input refresh time; 15ms or greater is recommended for normal inputs, 10ms for high speed inputs if the refresh time is reduced.

The following program is one example of how to do this.

Figure 6: Using the HKY instruction in an interrupt routine to speed up the input response.

If the use of ordinary inputs is too slow then it is possible to use the high speed inputs X0 to X7 (If they are not already used for another purpose). With the filter time set to approx 7ms (REFF instruction) and used with the timer interrupt routine, as explained above, the interrupt processing time can be set to 10ms for the HKY instruction.

# THE ADD INSTRUCTION (ADD, FNC 20) USED WITH THE M8023 FLOAT OPERATION FLAG

### Introduction

The FX PC family instruction set is divided into basic and applied instructions. The applied instructions provide powerful supplements to the basic set of PC instructions and give control over internal PC operations and external I/O. They are split into 10 groups, each group with a different application, eg. transfer of data within the PC.

Applied instructions 20 to 29 are concerned with Arithmetic and Logical Operations and are grouped under the heading of the same name.

This group includes the Add instruction (ADD, FNC 20). If Add is used with Auxiliary Relay M8023 (Float Operation Flag), then addition of floating point values is possible. M8023 must be turned on before the Add instruction is executed to allow this. This provides the facility to take floating point data from Data Registers, or Decimal and Hexadecimal constants and add similar data from a second source to it. The result is then stored in a destination device as a floating point value.

### The Add Instruction with M8023

The floating point form of the Add instruction has three parts:

Part 1: Set M8023

a) turn on M8023 to enable floating point operation.

Part 2: The Add instruction.

- b) the ADD statement itself

- c) the specification for the first Source Data, ie. the form of the data.

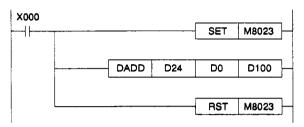

- **PARAMETERS** а M100 41 SET M8023 d b C е DADD D100 D110 D120 f RST M8023

Figure 1: The floating point Add instruction in ladder format.

- d) the specification for the second Source Data.

- e) the specification for the Destination Device, where the result will be stored.

Part 3: Reset M8023

f) turn off M8023 to disable floating point operation.

Figure 1 shows the typical appearance of a floating point Add instruction in a ladder program, while Figure 2 shows the same piece of ladder logic written in instruction format. This Add instruction would have the effect of adding the floating point value stored in Data Register pair D101 and D100 to the floating point value stored in D111 and D110 when Auxiliary Relay M100 is turned on. The floating point result would then be stored in D121 and D120. The following section explains each parameter in greater detail:

#### Parameter a) - Setting the float flag

The Float Operation flag M8023 must be SET to enable floating point calculations.

### Parameter b) - The ADD statement

The Add instruction can only be used in its DOUBLE word format if floating point values are being used. This is because floating point values are stored in a pair of Data Registers. An error will occur if this form is not used. This gives two different forms for the instruction:

DADD: The standard form of the instruction, taking 13 steps of program. In the example shown in Figure 1, while M100 is turned on, the DADD instruction will operate.

| PROGRAM<br>STEP<br>NUMBER | INSTRUCTION PROGRAM |   |      |

|---------------------------|---------------------|---|------|

| 0                         | LD                  | М | 100  |

| 1                         | SET                 | М | 8023 |

| 3                         | DADD                |   | 20   |

|                           |                     | D | 100  |

|                           |                     | D | 110  |

|                           |                     | D | 120  |

| 16                        | RST                 | М | 8023 |

Figure 2: The floating point Add instruction in instruction format.

# THE ADD INSTRUCTION (ADD, FNC 20) USED WITH THE M8023 FLOAT OPERATION FLAG

II) DADDP: The "P" suffix shows that DADD is being used in its PULSE format. The instruction will only operate when M100 provides a rising edge signal as it turns on. DADDP also takes 13 program steps.

### Parameter c) - Source Data 1

This identifies what form the Source Data takes.

The data can be one of the following: Decimal Values (K), Hexadecimal Values (H) or a pair of Data Registers (D) containing a floating point value. If K or H is used, then these values will be converted to floating point automatically.

### Parameter d) - Source Data 2

This identifies the second Source Data, which can be one of these forms:

Decimal Values (K), Hexadecimal Values (H) or Data Registers (D) holding a floating point value. Again, if K or H is used, then these values will be converted to floating point automatically.

### Parameter e) - Destination Devices

This identifies where the result will be stored. The Destination Devices can only be a pair of Data Registers, which store the sum as a floating point result.

**Notes:** The Destination Devices may be the same as one of the Source Devices. In this case, be careful to avoid unintentionally overwriting data.

The following combinations of Source Data are allowed:

| Source Data 1    | Source Data 2    |  |

|------------------|------------------|--|

| K/H              | K/H              |  |

| Floating Point D | Floating Point D |  |

| K/H              | Floating Point D |  |

| Floating Point D | K/H              |  |

### Parameter f)- Resetting the float flag

The Float Operation Flag must be reset to allow further functions to operate as normal. The flag can be left on if further operations requiring floating point calculations are needed. However, it is recommended that once all floating point functions are completed this flag should be switched off using RST.

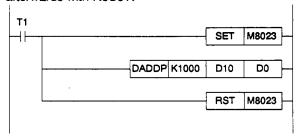

### Example Use of the Add Instruction with M8023

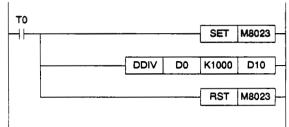

Figure 3 shows a typical use of the floating point Add instruction. In this case, DADDP is being used to add a fixed offset, K1000, to the floating point value held in D11 and D10 when T1 times out. The floating point sum is then stored in Data Registers D1 and D0. Using the PULSE instruction format ensures that the instruction will only execute once after T1's contacts close. Notice how the floating point operation is enabled before the Add instruction with SET and disabled afterwards with ReSeT.

Figure 3: Example ladder diagram for the floating point Add instruction.

# THE SUBTRACT INSTRUCTION (SUB, FNC 21) USED WITH THE M8023 FLOAT OPERATION FLAG

### Introduction

The FX PC family instruction set is composed of two sets of instructions; basic and applied. Applied instructions give control over internal PC operations and external I/O and provide powerful supplements to the basic set of PC instructions. They are split into 10 groups, each group with a different application, eg. transfer of data within the PC.

Applied instructions 20 to 29 perform Arithmetic and Logical Operations and are grouped under the heading of the same name.

This group includes the Subtract instruction (SUB, FNC 21). If Subtract is used with Auxiliary Relay M8023 (Float Operation Flag), then subtraction of floating point values is possible. M8023 must be turned on before the Subtract instruction is executed to allow this. This provides the facility to take floating point data from Data Registers, or Decimal and Hexadecimal constants and subtract similar data from a second source from it. The result is then stored in a destination device as a floating point value.

### The Subtract Instruction with M8023

The floating point form of the Subtract instruction has three parts:

Part 1: Set M8023

a) turn on M8023 to enable floating point operation.

Part 2: The Subtract instruction.

- b) the SUB statement itself

- c) the specification for the first Source Data, ie. the form of the data.

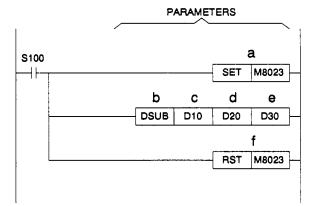

Figure 1: The floating point Subtract instruction in ladder format.

- d) the specification for the second Source Data.

- e) the specification for the Destination Device, where the result will be stored.

Part 3: Reset M8023

f) turn off M8023 to disable floating point operation.

Figure 1 shows the typical appearance of a floating point Subtract instruction in a ladder program, while Figure 2 shows the same piece of ladder logic written in instruction format. This Subtract instruction would have the effect of subtracting the floating point value stored in Data Register pair D21 and D20 from the floating point value stored in D11 and D10 when State S100 is turned on. The floating point result would then be stored in D31 and D30. The following section explains each parameter in greater detail:

### Parameter a) - Setting the float flag

The Float Operation flag M8023 must be SET to enable floating point calculations.

#### Parameter b) - The SUB statement

The Subtract instruction can only be used in its DOU-BLE word format if floating point values are being used. This is because floating point values are stored in a pair of Data Registers. An error will occur if this form is not used. This gives two different forms for the instruction:

DSUB: The standard form of the instruction, taking 13 steps of program. In the example shown in Figure 1, while S100 is turned on, the DSUB instruction will operate.

| PROGRAM<br>STEP<br>NUMBER | INSTRUCTION PROGRAM |   |      |

|---------------------------|---------------------|---|------|

| 0                         | LD                  | S | 100  |

| 1                         | SET                 | М | 8023 |

| 3                         | DSUB                | • | 21   |

|                           |                     | D | 10   |

| -                         |                     | D | 20   |

|                           |                     | D | 30   |

| 16                        | RST                 | М | 8023 |

Figure 2: The floating point Subtract instruction in instruction format.

## THE SUBTRACT INSTRUCTION (SUB, FNC 21) USED WITH THE M8023 FLOAT OPERATION FLAG

II) DSUBP: The "P" suffix shows that DSUB is being used in its PULSE format. The instruction will only operate when S100 provides a rising edge signal as it turns on. DSUBP also takes 13 program steps.

#### Parameter c) - Source Data 1

This identifies what form the Source Data takes.

The data can be one of the following: Decimal Values (K), Hexadecimal Values (H) or a pair of Data Registers (D) containing a floating point value. If K or H is used, then these values will be converted to floating point automatically.

#### Parameter d) - Source Data 2

This identifies the second Source Data, which can be one of these forms:

Decimal Values (K), Hexadecimal Values (H) or Data Registers (D) holding a floating point value. Again, if K or H is used, then these values will be converted to floating point automatically.

#### Parameter e) - Destination Devices

This identifies where the result will be stored. The Destination Devices can only be a pair of Data Registers, which store the result as a floating point value.

**Notes:** The Destination Devices may be the same as one of the Source Devices. In this case, take care to avoid accidentally overwriting data.

The following combinations of Source Data are allowed:

| Source Data 1    | Source Data 2    |

|------------------|------------------|

| K/H              | K/H              |

| Floating Point D | Floating Point D |

| K/H              | Floating Point D |

| Floating Point D | K/H              |

### Parameter f) - Resetting the float flag

The Float Operation Flag must be reset to allow further functions to operate as normal. The flag can be left on if further operations requiring floating point calculations are needed. However, it is recommended that once all floating point functions are completed this flag should be switched off using RST.

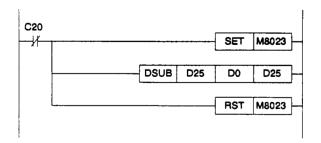

### Example Use of the Subtract Instruction with M8023

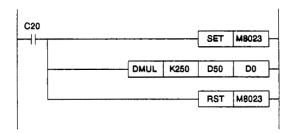

Figure 3 shows a typical use of the floating point Subtract instruction. For this example, DSUB is being used to subtract the floating point value held in D1 and D0 from that stored in D26 and D25. The floating point result is then stored in Data Registers D26 and D25 again. This instruction will execute until C20's contacts close. Notice how the floating point operation is enabled before the Subtract instruction with SET and disabled afterwards with ReSeT.

Figure 3: Example ladder diagram for the floating point Subtract instruction.

# THE MULTIPLY INSTRUCTION (MUL, FNC 22) USED WITH THE M8023 FLOAT OPERATION FLAG

### Introduction

The FX PC family has both basic and applied instructions. Applied instructions control both internal PC operations and external I/O and are powerful supplements to the basic PC set of instructions. They are split into 10 groups, each with a different application, eg. transfer of data within the PC.

Applied instructions 20 to 29 perform Arithmetic and Logical Operations and are grouped together under the same heading.

This includes the Multiply instruction (MUL, FNC 22). If Multiply is used with Auxiliary Relay M8023 (Float Operation Flag), then multiplication of floating point values is possible. M8023 must be turned on before the Multiply instruction is executed to allow this. This provides the facility to take floating point data from Data Registers, or Decimal and Hexadecimal constants and multiply it by similar data from a second source. The result is then stored in a destination device as a floating point value.

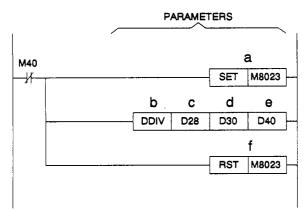

### The Multiply Instruction with M8023

The floating point form of the Multiply instruction has three parts:

Part 1: Set M8023

a) turn on M8023 to enable floating point operation.

Part 2: The Multiply instruction.

- b) the MUL statement itself

- c) the specification for the first Source Data, ie. the form of the data.

- d) the specification for the second Source Data.

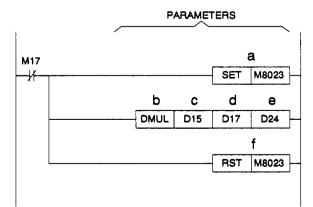

Figure 1: The floating point Multiply instruction in ladder format.

e) the specification for the Destination Device, where the result will be stored.

Part 3: Reset M8023

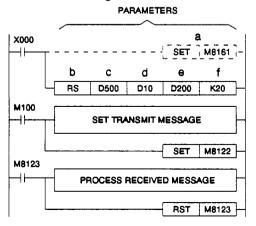

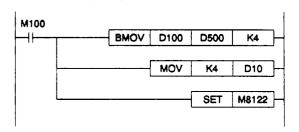

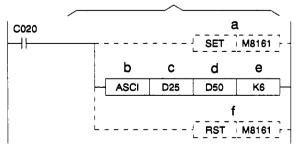

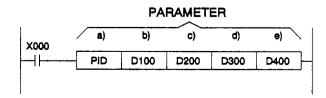

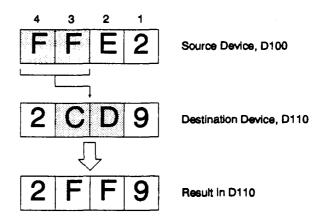

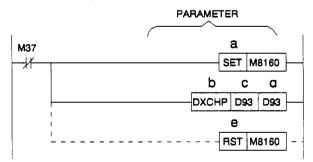

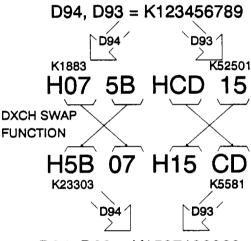

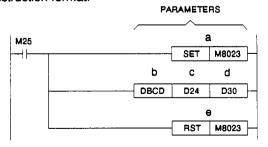

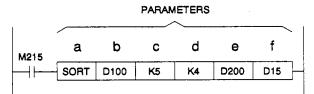

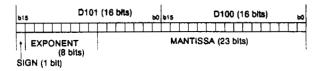

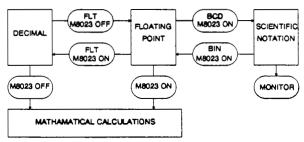

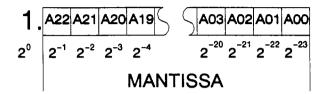

f) turn off M8023 to disable floating point operation.